Latest Highlights

A quick snapshot of what I’m focused on right now and the impact areas I care about.

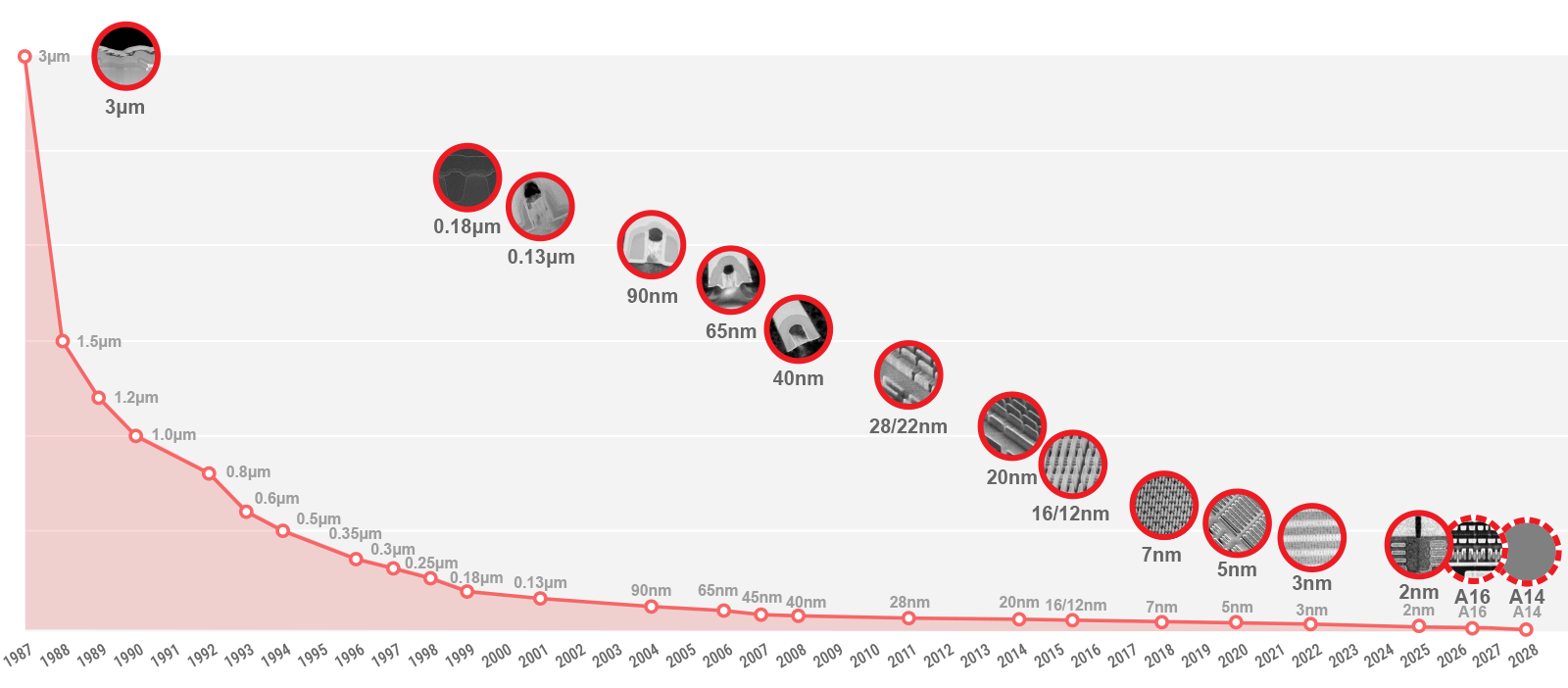

Sub-2nm Timing Closure

Driving timing closure for advanced test chips, balancing performance, power, and manufacturability.

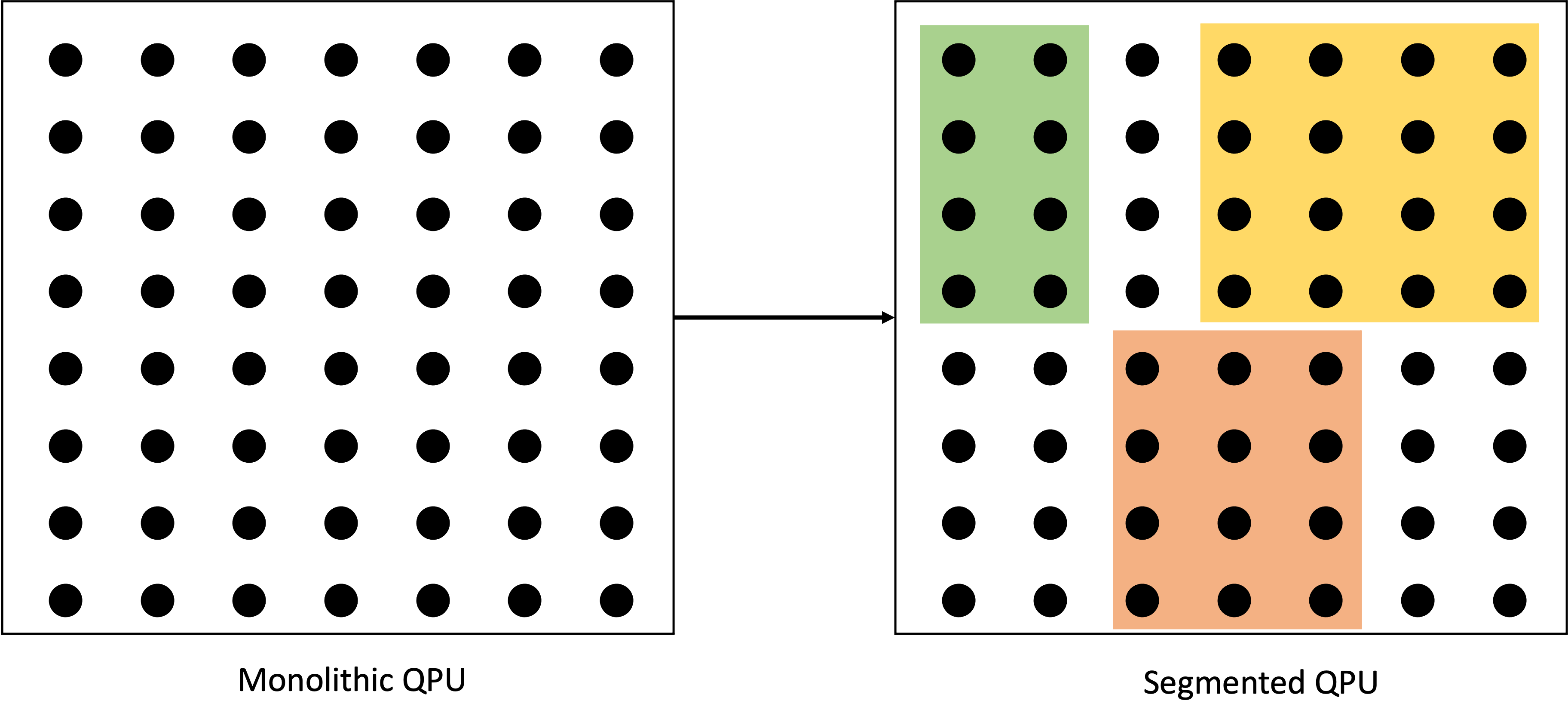

Quantum Hardware Focus

Exploring quantum device physics and scalable architectures for practical quantum computing.

Community & Mentorship

Contributing to Qiskit and engaging with the global community to grow quantum education.

About

I completed my Bachelor and Master of Technology in Electrical Engineering from the Indian Institute of Technology, Bombay in 2023.

Since Sep 2023, I have been working as a Static Timing Analysis Engineer at TSMC.

Electrical Engineering Senior & Quantum Computing Enthusiast

I am a 2023 graduate from IIT Bombay with a dual degree in Electrical Engineering, specializing in Microelectronics. Since Sep 2023, I have been working as a Static Timing Analysis Engineer at TSMC and have a keen interest in Quantum Computing and Quantum Information Science.

Currently Focused On

- Birthday: 27 March 2001

- Website: https://anda-creator.github.io

- Phone: +917319189316 / +8860911126108

- City: Hsinchu, Taiwan

- Age: 25

- Degree: Masters in EE

- Email: anuranan.fifa14@gmail.com

- Current Project: Working on a silicon test chip at TSMC as a STA engineer since Sep 2023.

Since Sep 2023, I have been working as a Static Timing Analysis Engineer at TSMC as my full-time job. Recently, I worked on a project involving timing closure for a sub-2 nm technology node for a TSMC internal test chip.

Introduction

This section contains a brief educational background and the roles I have held from college through my current professional journey.

Summary

Anuranan Das

Static Timing Analysis Engineer at TSMC • 2023 IIT Bombay Electrical Engineering Graduate

- Aastha, Ukilpara, Raiganj

- (+91) 7319189316

- anuranan.fifa14@gmail.com

Education

Electrical Engineering(Dual degree - B.Tech + Mtech) specializing in Microelectronics

2018 - 2023

IIT Bombay, Powai, Mumbai

Cumulative Performance Index(CPI): 9.07/10

Intermediate/+2

2016 - 2018

Ramakrishna Mission Vidyalaya,Narendrapur

Cumulative Performance Index(CPI): 95.60%

Matriculation

2016

Ramakrishna Mission Vidyalaya,Narendrapur

Cumulative Performance Index(CPI): 93.57%

Professional Experience

Static Timing Analysis Engineer

Sep'23 - Present

TSMC, Hsinchu, Taiwan

- Supporting advanced-node timing closure and signoff flows for internal silicon test chips.

- Partnering with cross-functional teams to improve STA methodology, reporting, and design quality.

Undergraduate Researcher

May'2019 - May'2023

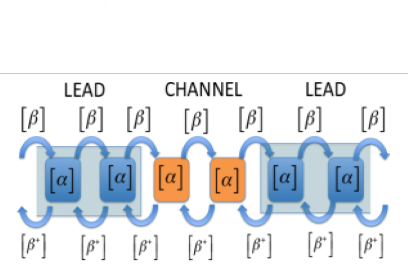

Computational Nanoelectronics & Quantum Transport Group, IITB

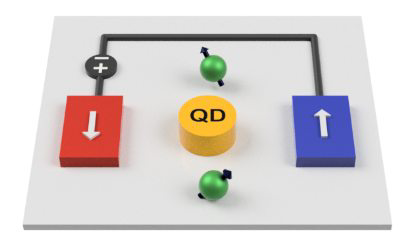

- Developed and analyzed an entanglement generating nanotransistor model with the help of ancilla impurities and Transport Master equations.

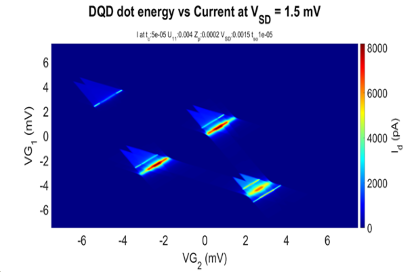

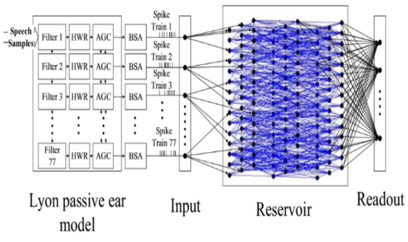

- Developing a CNN-based model to determine blockade states from charge stability diagrams and bias triangles for Silicon quantum dots.

Qiskit Advocate

Aug'21 - Present

- Succeeded in IBMQ Developer certification test and contributing to Qiskit SDK as an active community member.

MITACS Globalink Research Intern

May'22 - Jul'22

Simon Fraser University, Vancouver, BC, Canada

- Performed electrical characterization of suspended 𝑀𝑜𝑆2 NEMS to find resonant frequency and current-voltage characteristics.

Remote Junior Researcher

Sep'20 - Jan'21

UNSW, New South Wales, Australia

Projects

Here I have documented the major projects I have worked on until now. Projects are grouped by my college years and my current professional work.

- All

- Quantum

- Hardware

- Machine Learning

Professional Projects (2023 - Present)

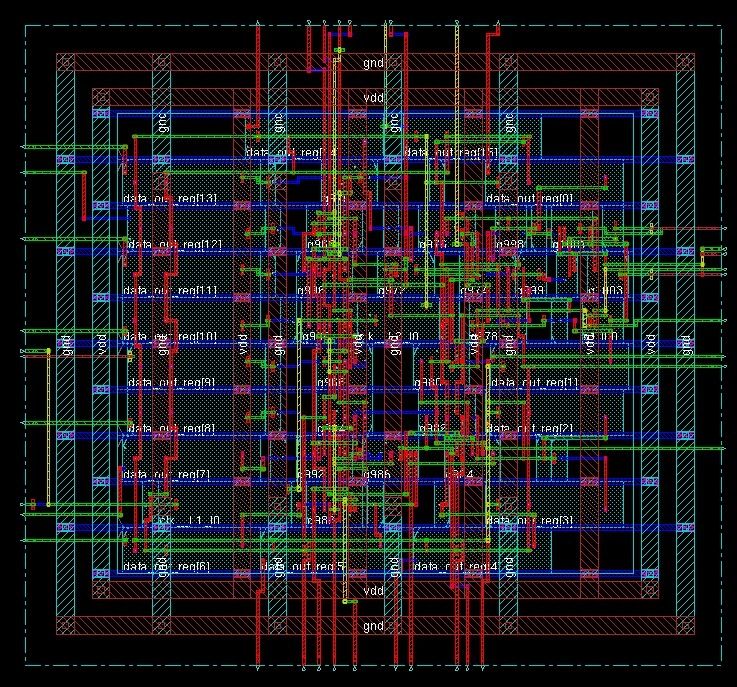

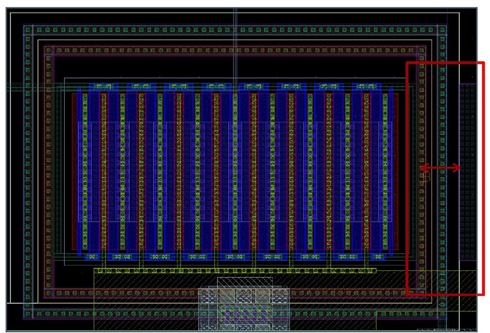

Due to NDA restrictions, I can only share high-level bullet points and visuals.

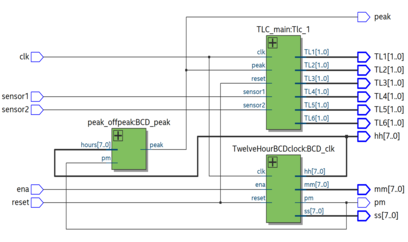

Advanced Node Timing Signoff ownership for internal Testchip

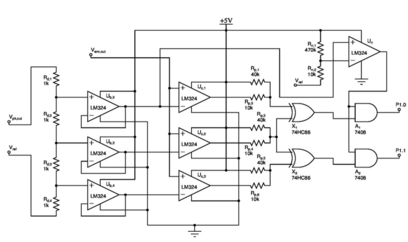

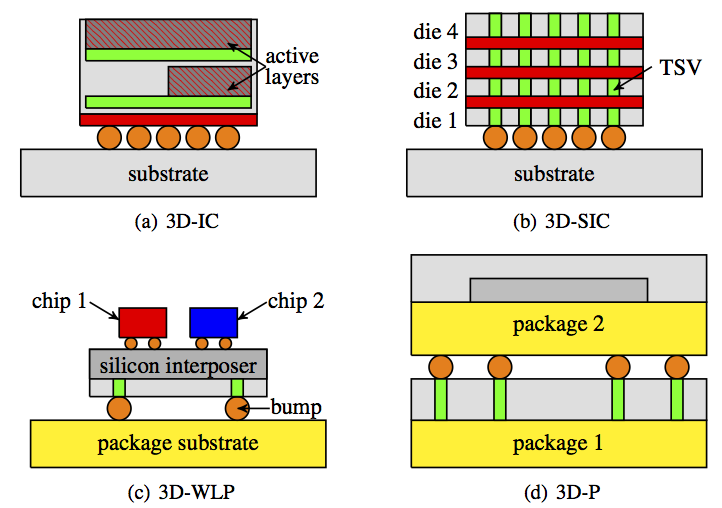

NDA • N3, N22 , < N2 technology nodes- 2D STA signoff owner-ship for Die to Die design in A16 technology node (< 2nm)

- 2D STA signoff support for 2 projects in N3 node and 1 project in N22 node

- 3D STA signoff support for 1 project in A16 technology node (< 2nm)

STA/CAD Automation & Flow Optimization for Testchip signoff

NDA • Python, TCL, Perl, JS development- Comprehensive Auto Tape Out Review generator development for 2D/3D STA and RC extraction flows with upto 90% automation

- Error/warning catching and JIRA-bound waiving methodology and utility for Testchip RCX/STA signoff

Physical Design (BackEnd) ownership in Advanced nodes (N3)

NDA • Innovus, Calibre, StarRC, PrimeTime- Design block PD owner for Testchip project responsible for Tapeout in N3 technology node

- Performed DRC cleaning and STA ECO for successful PV, STA and IREM signoff of design block

TSV Guard Ring impact on STA

NDA • Primetime, StarRC, spice, Innovus layout- Assesed impact of including Guard Ring around TSV on RC extraction and STA in advaned processed nodes (N3, N4)

- Performed STA and RCX correlation using exact matching methodology across pins and timing metrics to assess impact for both m-TSVs and s-TSVs

2D/3D STA Flow development

NDA • Primetime , Tempus , StarRC, QRC- Support development and maintainenance of TSMC internal testchip STA & RCX signoff flow.

- Contribute to building new QoR items to ensure full coverage of QC items in internal testchip timing signoff flow.

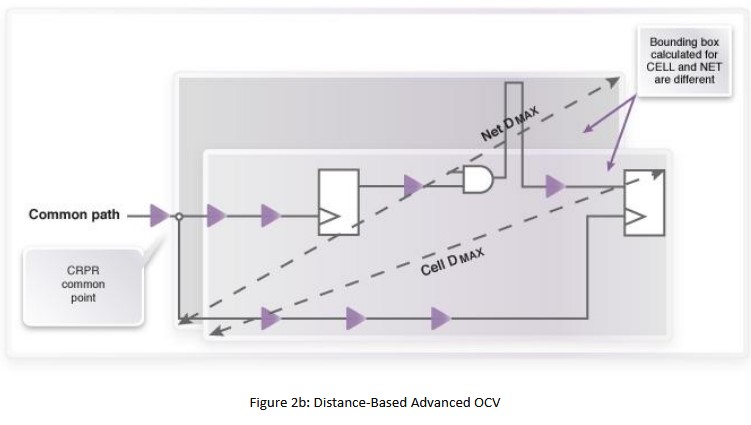

Timing Derate Validation Flow

NDA • Python, tcl, Primetime Scripting- Automation to effectively find out missed opportunities (MO) in derare application for internal STA flow

- Built flow to validate Vt-mistracking derate, SIR derate, distance derate, thermal derate effectively in flow

RC techfile Quality Ensuring

NDA • StarRC, QRC- Ensure RCX collateral quality for 3DFABRIC testcases like COWOS_L, COWOS_S , SoIC-X, SoW

- Check RC extracaction results for custom design using 3DFABRIC methodology.

Graduate and Undergraduate Projects (2018 - 2023)

Selected academic and research projects from IIT Bombay.

Publication and Preprints

Here are a list of Published and pre-prints which I worked on in my undergraduate years.

Steady-state tunable entanglement thermal machine using quantum dots

Published at Quantum Scinece and Technology, IOPscience (dated 23rd Sep, 2022)

Steady-State Tunable Entanglement Switch with Quantum Dots

Conference presentation at APS March Meetings, 2022

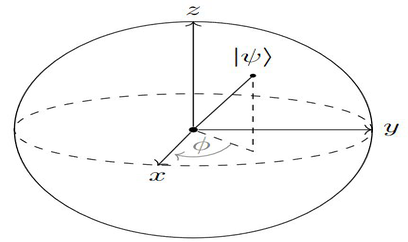

Euler-Rodrigues Parameters: A Quantum Circuit to Calculate Rigid-Body Rotations

Being Reviewed at IEEE Access

Machine learning unveils multiple Pauli blockades in the transport spectroscopy of bilayer graphene double-quantum dots

Published at APL Quantum (dated May 19, 2025)

Documents

Here is relevent bio, transcript available on request.

Contact

Feel free to contact me. I will get back to you as soon as possible.

Location:

Ukilpara, Raiganj, West Bengal, India (733134)

Call:

+91 7319189316